# Execution Optimization for SOC Using NOC

B. Reuben<sup>1</sup>, R. Arul Arumugam<sup>2</sup>

<sup>1</sup>AP/ECE, Department of ECE, Mahendra Institute of Technology, Namakkal Dt, Tamil Nadu, India <sup>2</sup>AP/ECE, Department of ECE, Annapoorna Engineering College, Salem Dt, Tamil Nadu, India Email address: revben @ mahendratech.org

Abstract— The developing intricacy in customer inserted items has prompted new propensities that gauge heterogeneous Multi-Processor Systems-On-Chip (MPSoCs) comprising of complex coordinated parts speaking with one another at rapid rates. Intercommunication necessities of MPSoCs made of many centers won't be doable utilizing a solitary shared transport or a progressive system of transports because of their poor versatility with framework measure, their mutual data transmission between all the joined centers and the vitality productivity prerequisites of definite items. Systems On-Chip (NoCs) have been proposed as a promising substitution to wipe out a significant number of the overheads of transports and MPSoCs associated by methods for universally useful correspondence designs that assistance to conquer the issues of adaptability and many-sided quality. This paper depicts that NoC assumes a basic job in upgrading the execution and power utilization and further improvement in execution can be acquired by utilizing information pressure.

**Keywords**— System on chip, Multiprocessor System on chip, Network on chip, Network interface, Network Interface compression, Electromagnetic interference, Non Uniform Cache Architecture.

### I. INTRODUCTION

In the most recent years there has been an expansion in calculation prerequisites for inserted frameworks because of the expanding unpredictability of new correspondence and interactive media measures. This has cultivated the improvement of superior implanted stages that can deal with the computational necessities of late complex calculations, which can't be executed in conventional installed monoprocessor designs. To meet the developing calculation serious applications and the necessities of low-control, elite frameworks, the quantity of processing assets in single-chip has tremendously expanded, in light of the fact that current VLSI innovation can bolster such a broad coordination of transistors. By including many registering assets, for example, CPU, DSP, particular IPs, and so forth to assemble a framework in System-on-Chip, its interconnection between one another turns into another testing issue. Despite the fact that MPSoCs guarantee to essentially enhance the handling abilities and adaptability of inserted frameworks, one noteworthy issue in their present and future plan is the adequacy of the interconnection systems between the inward segments, as the measure of parts develops with each new mechanical hub. Transport based plans are not ready to adapt the heterogeneous and requesting correspondence to prerequisites of MPSoCs. In most System-on-Chip applications, a common transport interconnection which needs discretion rationale to serialize a few transport get to demands, is received to speak with each coordinated handling unit due to its ease and basic control qualities. In any case, such shared transport interconnection has some restriction in its versatility on the grounds that just a single ace at any given moment can use the transport which implies all the transport gets to ought to be serialized by the judge. In this way, in such a situation where the quantity of transport requesters is vast and their required data transfer capacity for interconnection is more than the present transport, some other interconnection techniques ought to be considered. Such adaptable data transfer capacity prerequisite can be fulfilled by utilizing onchip bundle exchanged smaller scale system of interconnects, for the most part known as Network-on-Chip (NoC) design. The versatile and secluded nature of NoCs and their help for proficient on-chip correspondence prompt NoC-based framework executions. Despite the fact that the present system innovations are very much created and their supporting highlights are phenomenal, their confounded designs and usage multifaceted nature make it difficult to be embraced as an on-chip interconnection technique. Subsequently, new standards and philosophies that can configuration control compelling and solid interconnect for MPSoCs are an absolute necessity these days. Systems on-Chip (NoCs) have been proposed as a promising answer for the previously mentioned versatility issue of imminent MPSoCs. NoCs additionally help in handling plan unpredictability and confirmation issues. Utilizing NoCs the interconnect structure and wiring intricacy can be controlled well. At the point when the interconnect is organized, the quantity of timing infringement that happen amid the physical outline (floor arranging and wire steering) stage are insignificant. Such plan consistency is basic for the present MPSoCs to accomplish timing conclusion. It prompts quicker plan cycle and quicker time-to-showcase.

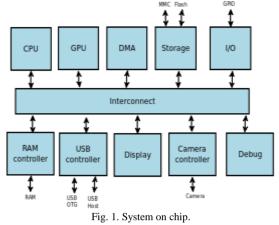

### II. SYSTEM-ON-CHIP

Multi-processor System- on- Chip (MPSoC) are SoC that may contain at least one sorts of registering subsystems, recollections, input/yield gadgets (I/O), and different peripherals, as in [1]. The MPSoC engineering is made of three kinds of segments: programming subsystems, equipment subsystems, and between subsystem correspondence .The equipment subsystems (HW-SS) speak to custom equipment subsystems that execute particular usefulness of an application or worldwide memory sub frameworks. The HW-SS contain two kinds of segments: intra-subsystem correspondence and particular equipment segments. The equipment segments actualize particular elements of the objective application or speak to worldwide recollections open by the figuring subsystems. The intra-subsystem correspondence speaks to the

correspondence inside the HW-SS between the diverse equipment segments. This can be in type of a little transport (gathering of parallel wires for transmitting address, information, and control flags) or point-to-point correspondence joins. The product subsystems (SW-SS) speak to programmable subsystems, likewise called processor hubs of the engineering. The SW-SS incorporate figuring assets, intra-subsystem correspondence, and other equipment segments, for example, neighborhood recollections, I/O parts, or equipment quickening agents.

The registering assets speak to the preparing units or CPUs. The CPU (focal preparing unit) otherwise called processor center, handling component, or without further ado processor executes programs put away in the memory by getting their guidelines, inspecting them, and afterward executing them in a steady progression as in [1], [5]. There are two kinds of SW-SS: single center and multi-center. The single-center SW-SS incorporates a solitary processor, while the multi center SW-SS can coordinate a few processor centers in a similar subsystem, more often than not of same sort. The intra-subsystem correspondence speaks to the correspondence inside the SW-SS, e.g., nearby transport, equipment FIFO, point-to-point correspondence joins, or other neighborhood interconnection organize used to interconnect the diverse equipment segments inside the SW-SS. Homogeneous MPSoC as in [8] models are made of indistinguishable programming subsystems consolidating a similar kind of processors. In the heterogeneous MPSoC designs, distinctive sorts of processors are incorporated on a similar chip, bringing about various kinds of programming subsystems. These can be GPP (broadly useful processor) subsystems for control tasks of the application; DSP (advanced flag processor) subsystems exceptionally custom-made for information escalated applications, for example, flag handling applications; or ASIP (application-particular guidance set processor)subsystems with a configurable guidance set to fit particular elements of the application. The distinctive subsystems working in parallel on various parts of a similar application must impart each other to trade data. There are two unmistakable MPSoC outlines that have been proposed and actualized for the correspondence models between the subsystems: shared memory and message passing. The common memory correspondence show portrays the homogeneous MPSoC engineering. The key property of this class is that correspondence happens certainly. The correspondence between the distinctive CPUs is made through a worldwide shared memory. Any CPU can read or compose an expression of memory by simply executing LOAD and STORE guidelines. Other than the regular memory, every processor code may have some nearby memory which can be utilized for program code and those things that need not be shared. For this situation, the MPSoC design executes a multithreaded application sorted out as a solitary programming stack. The message-passing association expect numerous product stacks running on indistinguishable or nonindistinguishable programming subsystems. The correspondence between various subsystems is by and large made through message passing. The key property of this class is that the correspondence between the distinctive processors

is express through I/O activities. The CPUs impart by sending each other message by utilizing natives, for example, send and get.

Multiprocessor structures and stages have been acquainted with expand the materialness of Moore's law. They rely upon simultaneousness and synchronization in both programming and equipment to improve the outline efficiency and framework execution. These stages will likewise need to fuse very adaptable, reusable, unsurprising, cost and vitality productive structures. With the quickly moving toward billion transistors time a portion of the primary issues will emerge from non-adaptable wire delays, blunders in flag trustworthiness and unsynchronized correspondences. The MPSoC engineering is made of three sorts of parts: programming subsystems, equipment subsystems, and between subsystem correspondence. The equipment subsystems (HW-SS) speak to custom equipment subsystems that execute particular usefulness of an application or worldwide memory subsystems. the HW-SS contain two kinds of segments: intra-subsystem correspondence and particular equipment segments. The equipment segments execute particular elements of the objective application or speak to worldwide recollections available by the figuring subsystems.

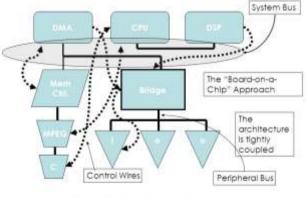

A. Traditional SoC nightmare

Fig. 2. Traditional SoC nightmare.

As found in figure no.2 the point to point correspondence results in correspondence bottleneck. Transport based correspondence is additionally found in the figure .Both the

B. Reuben and R. Arul Arumugam, "Execution optimization for SOC using NOC," International Journal of Multidisciplinary Research and Publications (IJMRAP), Volume 1, Issue 4, pp. 9-13, 2018.

ISSN (Online): 2581-6187

sorts of correspondence between the bocks results in correspondence bottleneck. Thus correspondence and calculation can't be isolated. In this way the execution, speed and power utilization are unfavorably influenced.

## B. Limitations of SoC

- 1) Needs assortment of interfaces

- 2) Poor detachment among calculation and correspondence

- 3) Design many-sided quality

## III. NETWORK-ON-CHIP

On a billion transistors chip, it may not be conceivable to send a worldwide flag over the chip inside constant limits. As the quantity of IP modules in Systems-on-Chip (SoCs) builds, transport based interconnection structures may keep these frameworks to meet the execution required by numerous applications. For frameworks with concentrated parallel correspondence prerequisites transports may not give the required data transmission, idleness, and power utilization. An answer for such a correspondence bottleneck is the utilization of an installed exchanging system, called Network-on-Chip (NoC), to interconnect the IP modules in SoCs. NoCs configuration space is impressively bigger when contrasted with a transport based arrangement, as various steering and intervention procedures can be actualized and distinctive associations of the correspondence framework. In the event that the SoC (System-on-Chip) is synchronized by a worldwide clock flag, the circuit will be more inclined to EMI (electromagnetic obstruction). The conventional framework outlines are generally founded on basic ways and clock trees. These basic ways and clock trees add to an expanded measure of intensity utilization. Along these lines, SoCs are not control productive. Furthermore, it is hard to deal with these clock trees because of clock skew issues.

## Fundamental Properties of the NoC Worldview

The fundamental properties of the NoC worldview are recorded beneath

1) Separates correspondence from calculation.

2) Avoids worldwide, brought together controller for correspondence.

3) Allows self-assertive number of terminals.

4) Topology permits the expansion of connections as the framework measure develops (offers versatility).

5) Customization (interface width, support sizes, even topology).

6) Allow numerous voltage and recurrence areas.

7) Delivers information all together either normally or by means of layered conventions.

8) To emotionally supportive network testing.

Consequently, the NoC assumes a basic job in upgrading the execution and power utilization of such non-uniform reserve based multicore structures.

## A. Basic building squares of Network on chip

A system on-chip is made out of three primary building squares.

1) Links

### 2) Router

3) Network interface or Network connector

1) Links: A correspondence interface is made out of an arrangement of wires and associates two switches in the system. Connections may comprise of at least one intelligent or physical channels and each channel is made out of an arrangement of wires. In the rest of the sections, except if expressed something else, the words net, wire, and line mean a solitary wire interconnecting two elements (switches and additionally IP centers). The words channel and connection mean a gathering of wires associating two elements. Regularly, a NoC interface has two physical channels making a full-duplex association between the switches (two unidirectional diverts in inverse directions). The number of wires per channel is uniform all through the system and is known as the channel bit width. The usage of a connection incorporates the meaning of the synchronization convention among source and target hubs. This convention can be executed by devoted wires set amid the correspondence or through different methodologies, for example, FIFOs. Nonconcurrent joins are additionally a fascinating alternative to execute universally offbeat locally synchronous (GALS) frameworks where neighborhood handshake conventions are accepted. The connections at last characterize the crude execution (because of connection postponements) and power utilization in a NoC and planners assumed give quick, solid, and low-control interconnects between hubs in the system.

2) Routers: The plan and execution of a switch requires the meaning of an arrangement of approaches to manage bundle impact, the steering itself, et cetera. A NoC switch is made out of number of information ports (associated with shared NoC channels), number of yield ports (associated with potentially other shared channels), exchanging lattice interfacing the information ports to the yield ports, and neighborhood port to get to the IP center associated with this switch. Notwithstanding this physical association foundation, the switch additionally contains a rationale hinder that executes the stream control strategies (directing, mediator, and so forth.) and characterizes the general technique for moving information however the NoC. A stream control arrangement portrays the bundle development along the NoC and all things considered it includes both worldwide (NoC-level) and neighborhood (switch level) issues. One can guarantee a stop free directing, for example, by taking particular measures in the stream control approach (by maintaining a strategic distance from specific ways inside the NoC for instance). Control can be of two sorts - incorporated and dispersed. NoCs commonly utilize a conveyed control, where every switch settles on choices locally. Stop happens when arrange assets are completely possessed and sitting tight for one another to be discharged to continue with the correspondence, that is, when two ways are hindered in a cyclic manner when the status of the assets continue changing (there is no halt) however the correspondence isn't finished. Steering calculation is the rationale that chooses one yield port to forward a parcel that touches base at the switch input. Directing calculations can prompt or maintain a strategic

distance from the event of stops and live bolts. While the directing calculation chooses a yield port for a parcel, the assertion rationale actualized in the switch chooses one info port when different bundles land at the switch all the while asking for a similar yield port.

3) Network Interface: The third NoC building square is the system connector (NA) or system interface (NI). This square makes the rationale association between the IP centers and the system, since every IP may have an unmistakable interface convention concerning the system. This square is vital on the grounds that it permits the division among calculation and correspondence. This permits the reuse of both, center and correspondence framework free of one another. The connector can be separated into two sections: front end and back end. The front end handles the center demands and is in a perfect world unconscious of the NoC. The back end part handles the system convention (amasses and dismantles the parcel, reorders cushions, actualizes synchronization conventions, helps the switch regarding capacity, and so on.).

#### B. NoC Performance Parameters

The execution of a system on-chip can be assessed by three parameters:

- 1) Bandwidth

- 2) Throughput

- 3) Latency

1) Bandwidth: Bandwidth alludes to the most extreme rate of information spread once a message is in the system. The unit of measure for data transfer capacity is bit every second (bps) and it for the most part thinks about the entire parcel, including the bits of the header, payload and tail.

2) Throughput: Throughput is characterized as the most extreme movement acknowledged by the system, that is, the greatest measure of data conveyed per time unit. The throughput measure is messages every second or messages per clock cycle. One can have a standardized throughput (autonomously from the extent of the messages and of the system) by isolating it by the measure of the messages and by the span of the system. Subsequently, the unit of the standardized throughput is bits per hub per clock cycle (or every second).

3) Latency: Latency is the time slipped by between the start of the transmission of a message (or parcel) and its entire gathering at the objective hub. Dormancy is estimated in time units and for the most part utilized as examination premise among various outline decisions. For this situation, inactivity can likewise be communicated as far as test system clock cycles. Regularly, the dormancy of a solitary bundle isn't significant and one uses the normal idleness to assess the system execution.

### C. Data pressure system for NoC

The pattern towards coordinating various centers on a similar pass on has emphasized the requirement for bigger onchip stores. Huge reserves are built as a huge number of littler store banks interconnected through a bundle constructed Network-in light of Chip (NoC) correspondence texture. NoC

assumes a basic job in advancing the execution and power utilization of non-uniform reserve based multicore models. We analyze the information pressure procedure Compression in the NIC (NC).Higher frequencies prompt higher power utilization, which, thusly, brought forth cooling and unwavering quality issues. By using various less difficult, smaller centers on a solitary bite the dust, engineers would now be able to give Thread-Level Parallelism (TLP) at much lower frequencies. The nearness of a few handling units on a similar pass on requires larger than usual L2 and, where material, L3 reserves to suit the necessities all things considered. Bigger reserve sizes are effortlessly encouraged by the before said blast in on-chip transistor checks. Notwithstanding, the usage of such extensive store recollections could be blocked by inordinate interconnect delays. While littler innovation hubs are related with shorter entryway delays, the previous are likewise in charge of expanding worldwide interconnect delays [1]. Thusly, the conventional suspicion that each level in the memory chain of importance has a solitary, uniform access time is not any more legitimate.

## IV. CONCLUSION

Intercommunication necessities of MPSoCs made of several centers won't be doable utilizing a solitary shared transport or a progression of transports because of their poor adaptability with framework estimate, their common data transfer capacity between all the appended centers and the vitality productivity. NoC isolates correspondence from calculation, concentrated controller for correspondence, permits discretionary number of terminals. It has a topology that permits the expansion of connections as the framework measure develops (offers adaptability), does not use long, worldwide wires traversing the entire chip .When contrasted with transport based correspondence NoC gives numerous focal points like execution does not minimize with organize scaling, assertion also, directing are dispersed, different jumps increment dormancy and so on. Information pressure is utilized to lessen arrange stack, to bring down the power utilization. The NIC conspire on a normal gives decrease in control utilization.

#### REFERENCES

- T. R. Parthasarathy, N. Venkatakrishnan, and K. Balamurgan, "Analysis of partioning between ARM and FPGA on performance characteristics," *IEEE International Conference on Advanced Communication Control* and Computing Technologies, 2012.

- [2] Q. Meng, Z. Li, and F. Wang, "Functional verification of external memory interface IP core based on restricted random testbench," *International conference on computer Engineering and Technology*, 2010.

- [3] P. Chen., Y. T. Yeh, C. H. Chen, J. C. Yeh, and C. W. Wu, J. s. Lee, and Y. C. Lin "An enhanced EDAC methodology for low power PSRAM," *IEEE International Test Conference*, 2006.

- [4] F. Corno, M. R. Sonza, G. Squillero, and M. Violante, "On the test of microprocessor IP cores," in *Proc. Des. Autom. Test Eur.*, pp. 209–213, 2001.

- [5] N. Kranitis, A. Paschalis, D. Gizopoulos, and G. Xenoulis, "Software based self-testing of embedded processors," *IEEE Trans. Comput.*, vol. 54, no. 4, pp. 461–475, 2005.

- [6] K. Jayaraman, V. M. Vedula, and J. A. Abraham, "Native mode functional self-test generation for systems-on-chip," in *Proc. Int. Symp.*

- *Quality Electron. Des.* pp. 280–285, 2002. S. Hwang and J. A. Abraham "Reuse of addressable system bus for SoC [7] testing," Proc. IEEE Int. ASIC/SoC Conf., pp. 215-219, 2001.

- IEEE Standard Testability Method for Embedded Core-Based Integrated [8] Circuits, 1500- 2005, 2005. Available: http://www.ieee.org

- [9] R. Huang, M. K. Iyer, and K. T. Cheng, "A self-test methodology for IP cores in bus-based programmable SoCs," in *Proc. IEEE VLSI Test Symp.*, pp. 198–203, 2001.

- [10] K. Gupta and Prof. R. L. Dua, "30 BIT hamming code for error detection and correction with even parity and odd parity check method by using VHDL," International Journal of Computer Applications, vol. 35, no. 13, pp. 31-38, 2011.[11] R.W. Hamming, "Error correcting and error detecting codes," *Bell Sys.*

- Tech. Journal, vol. 29, pp. 147-160, 1950.